-

Linh kiện PC

VGA Nvidia RTX 5090/ 5090 Ti RTX 5080/ 5080 Ti RTX 5070/ 5070 Ti RTX 5060/ 5060 Ti RTX 5050 / 5050 Ti RTX 4090/ 4090Ti RTX 4080 / 4080 Super RTX 4070 / 4070 Super RTX 4060 / 4060Ti RTX 4000 series GTX 1660 series RTX 20 series VGA LEADTEK NVIDIA QUADRO NVIDIA RTX PROVGA AMD RX 9000 Series RX 7000 Series RX 6900 XT / 6950 XT RX 6800 / 6800 XT RX 6700 XT / 6750 XT RX 6600 / 6600 XT / 6650 XT RX 6500 XT RX 6400 / 6400 XT RX 5000 Series RX 500 Series Radeon ProMainboard - Bo mạch chủ Intel Z890 Intel Z790 Intel B760M Intel Z690 Intel Z590 Intel B860M Intel B660 / H610 Intel B560 / H510 AMD X870 AMD B850 AMD B840 AMD X670 / X670E AMD B650 AMD B550 / A520 AMD X570 AMD X470 / B450 AMD TRX40 AMD A620MTản Nhiệt Cooling Nước Tản Nhiệt Quạt Tản Nhiệt Tản Nhiệt Khí Tản Nhiệt Nước AIO Phụ Kiện Cooling Keo tản nhiệtRAM - Bộ nhớ trong Ram Corsair Ram Klevv Ram Thermaltake Ram TeamGroup Ram OCPC Ram Gigabyte Ram G.Skill Ram Khác RAM Samsung RAM Laptop RAM CrucialCase - Vỏ máy tính Case LIAN-LI Case CORSAIR Case Phanteks Case Asus Case NZXT Case Cooler Master Case InWin Case Antec Case MSI Case Thermaltake Case Xigmatek Case Cougar Case khác Case MIK Case Deepcool Case ADATA CASE 1ST PLAYER Case GIGABYTE Case HYTE CASE GAMDIAS Case Fractal Design Case Segotep CASE Montech Case JonsboPSU - Nguồn Máy Tính PSU Corsair PSU Coolermaster PSU Asus PSU FSP PSU Gigabyte PSU Antec PSU SilverStone PSU Super Flower PSU MSI PSU Thermaltake PSU Xigmatek PSU Hãng Khác PSU Dragon PSU MIK PSU AEROCOOL PSU DeepCool PSU NZXT PSU ADATA PSU LEADEX PSU Segotep PSU Phanteks

- Loa - Đồ công nghệ

-

Màn Hình Máy Tính

Thương hiệu màn hình Màn hình ASUS Màn hình MSI Màn Hình Viewsonic Màn Hình LG Màn Hình Samsung Màn Hình HKC Màn Hình Dell Màn Hình HP Màn Hình AOC Màn hình Gigabyte Màn hình BenQ Màn hình Acer Màn hình Cooler Master Màn Hình Philips Màn hình Lenovo Màn hình Apple Màn hình Galax Màn hình KTCTần số quét màn hình Màn hình 280Hz Màn hình 240Hz Màn hình 180Hz Màn hình 165Hz Màn hình 144Hz Màn hình 120Hz Màn hình 100Hz Màn hình 75Hz Màn hình 60HzKích cỡ màn hình Màn hình 49 ~ 65 inch Màn hình 34 ~ 49 inch Màn hình 27 ~ 32 inch Màn hình 23 ~ 25 inch Màn hình 19.5 ~ 22 inch Màn hình dưới 19 inch

-

Gaming Gear

Bàn phím cơ Gaming Bàn phím Ducky Bàn phím Khác Bàn phím Akko Bàn phím RAZER Bàn phím Corsair Bàn phím Logitech Bàn phím SteelSeries Bàn phím Dareu Bàn phím Keychron Bàn phím Thermaltake Bàn phím ASUS Bàn phím MSI Bàn phím cơ Deepcool Bán phím NZXT Bàn phím ADATA Bàn phím IQUNIX Bàn phím cơ MicroPack Bàn phím Keydous Bàn phím Microsoft Bàn Phím MIKIT Bàn phím Glorious Bàn phím Angry Miao Bàn phím cơ FL-Esports Bàn phím Cơ Cooler Master Phụ Kiện Bàn PhímChuột Gaming Chuột Razer Chuột E-Dra Chuột Logitech Chuột Corsair Chuột Steelseries Chuột MIK Chuột AKKO Chuột DareU Chuột Thermaltake Chuột ASUS Chuột Deepcool Chuột NZXT Chuột ADATA Chuột Pulsar Chuột Cooler Master Chuột BenQ Chuột Glorious Chuột MicropackBàn di chuột HyperX E-Dra Corsair RAZER AKKO Steelseries Thermaltake Asus Logitech NZXT Bàn di chuột HyperWorkTai nghe Gaming Tai nghe HyperX Tai nghe Zidli Tai nghe Corsair Tai nghe Razer Tai nghe SteelSeries Tai nghe Dareu Tai nghe Asus Tai nghe JBL Tai Nghe Thermaltake Tai nghe Akko Tai nghe Sennheiser Tai nghe Logitech Tai nghe Cooler Master Tai nghe ADATA Tai nghe Eaglend Tai nghe Beyerdynamic Tai nghe Ultrasone Tai nghe AG-Final Tai Nghe Gaming Angry Miao Tai nghe MCHOSE

- Tản Nhiệt Nước

- Modding PC

-

Bàn Ghế Cao Cấp

Ghế Gaming Ghế gaming E-Dra Ghế gaming Corsair Ghế gaming Cougar Ghế Gaming Asus Ghế gaming AKRacing Ghế gaming DXRacer Ghế Gaming Warrior Ghế gaming Aerocool Ghế Gaming Thermaltake Ghế gaming Secretlab Ghế Gaming Cooler Master Ghế Gaming Andaseat Ghế Gaming Razer Ghế Gaming VertagearBàn Gaming Bàn DXRACER Bộ chân bàn Ergonomic Bàn Warrior Bàn Thermaltake Bàn Gaming Cooler Master Bàn nâng hạ

- MiniPC/ Office PC

- Laptop

- Thiết bị mạng

PCIE 7.0 ĐẠT TỚI 512 GB/S, RA MẮT VÀO NĂM 2025 !!!

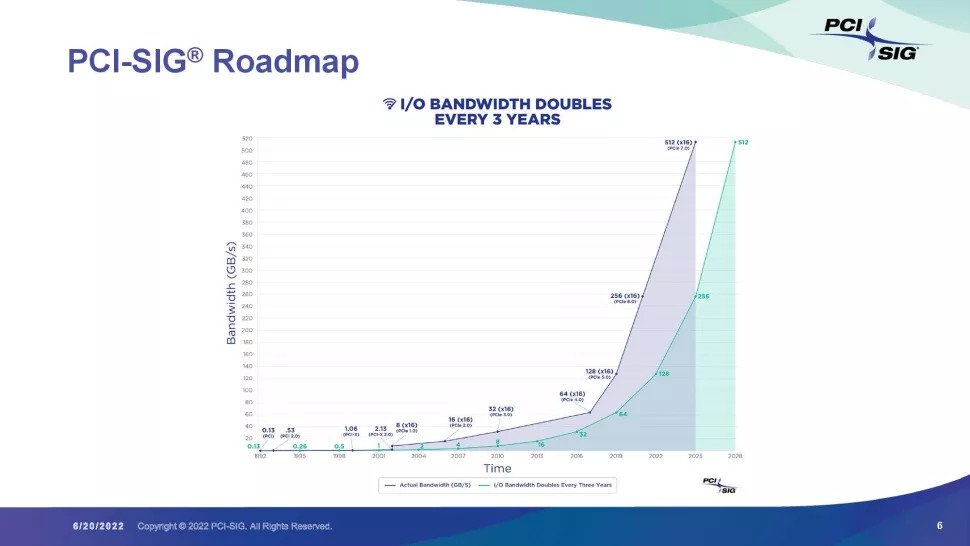

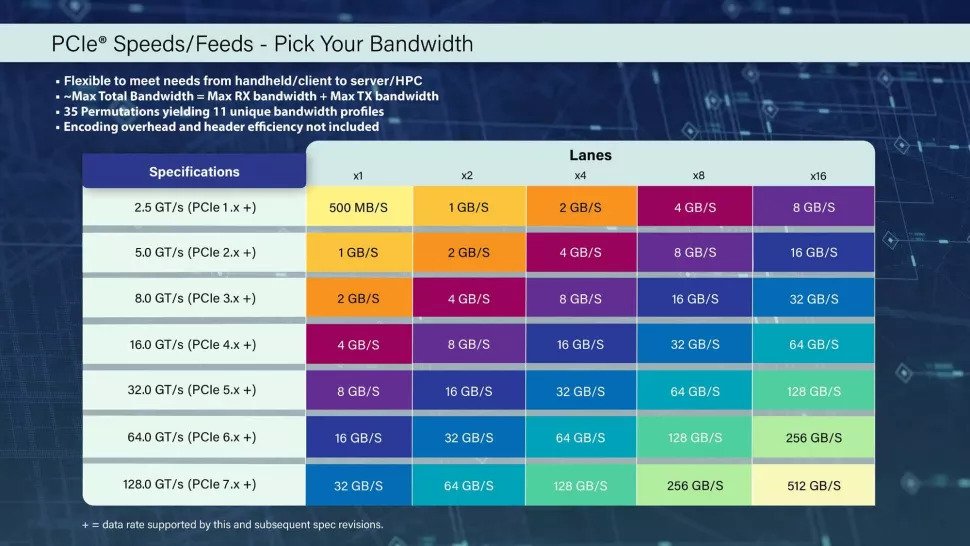

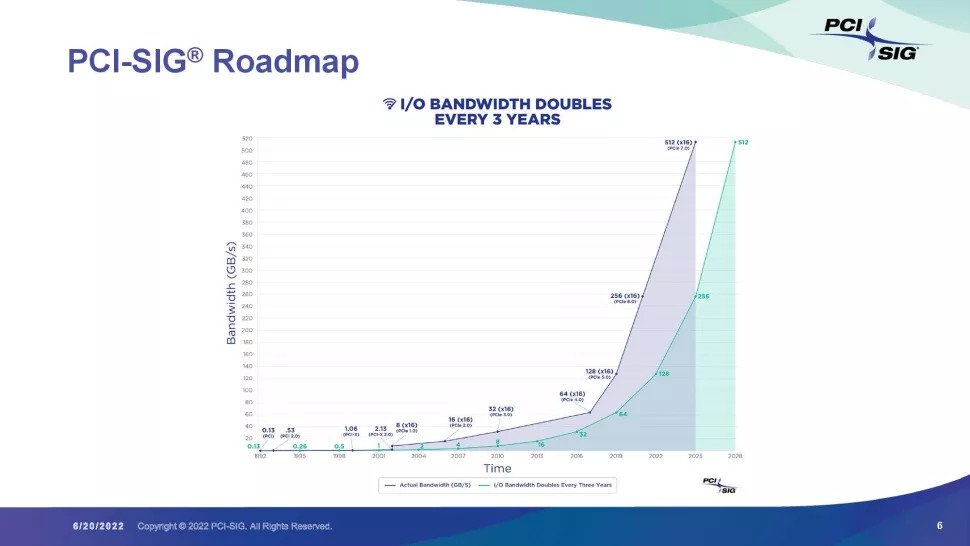

Hội nghị các nhà phát triển PCI-SIG 2022 đang diễn ra sôi nổi và hôm nay, ủy ban tiêu chuẩn đằng sau giao diện PCIe phổ biến đã thông báo rằng thông số kỹ thuật PCIe 7.0 được nhắm mục tiêu phát hành cho các thành viên vào năm 2025 với tốc độ dữ liệu lên đến 128 GT / s. Điều đó tương đương với 512 GB / s thông lượng hai chiều thông qua kết nối 16 làn (x16), trước khi mã hóa chi phí. Xin nhắc lại, PCI-SIG là tổ hợp đứng sau giao diện PCIe, một tiêu chuẩn công nghiệp mở bao gồm hơn 900 công ty thành viên.

PCI-SIG lưu ý rằng giao diện PCIe 7.0 sẽ cung cấp thông lượng hai chiều 512 GB / s qua kết nối x16, nhưng đó là trước khi mã hóa chi phí và tác động của hiệu quả tiêu đề, cả hai đều ảnh hưởng đến băng thông có thể sử dụng.

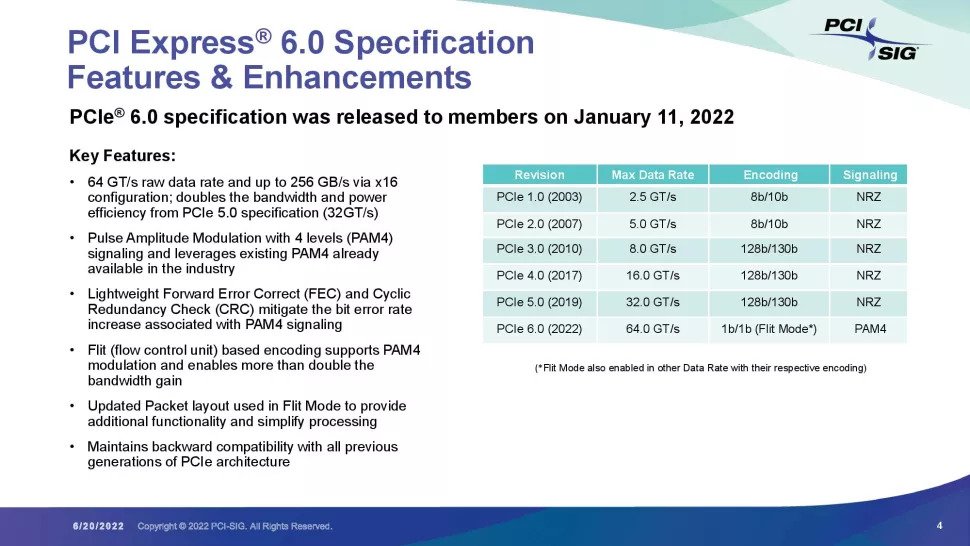

Giao diện PCIe 7.0 sẽ tiếp tục sử dụng mã hóa chế độ flit 1b / 1b và công nghệ tín hiệu PAM4 được giới thiệu với PCIe 6.0, một cải tiến đáng chú ý so với mã hóa 128b / 130b và tín hiệu NRZ được sử dụng với các thông số kỹ thuật 3.0 đến 5.0. Do đó, băng thông có thể sử dụng trong thế giới thực sẽ thấp hơn một chút so với con số 512 GB / s nhưng vẫn tăng gấp đôi so với giao diện PCIe 6.0.

Như chúng ta đã thấy với việc chuyển sang PCIe 4.0 và 5.0, độ dài của các khe PCIe sẽ lại rút ngắn do tốc độ truyền tín hiệu nhanh hơn. Điều này có nghĩa là khoảng cách tối thiểu cho phép mà không có thành phần bổ sung giữa thiết bị gốc PCIe, như CPU và thiết bị cuối, như GPU, sẽ ngắn lại. Do đó, các bo mạch chủ sẽ cần nhiều retimer hơn và PCB dày hơn bao gồm các vật liệu chất lượng cao hơn chúng ta đã thấy ở các thế hệ giao diện trước và hỗ trợ PCIe 7.0 sẽ dẫn đến một đợt tăng giá bo mạch chủ nữa.

Đáng chú ý, băng thông cao hơn trên mỗi làn, hiện ở mức 32 GB / s hai chiều cho kết nối x1, có thể cho phép kết nối 'mỏng hơn' đối với một số thiết bị (chẳng hạn như sử dụng x4 thay vì kết nối x8).

Cơ sở cho thông số kỹ thuật PCIe 7.0 xuất phát sau khi PCI-SIG hoàn thiện thông số kỹ thuật PCIe 6.0 vào đầu năm nay và sẽ cung cấp băng thông tăng gấp đôi so với giao diện PCIe 6.0 thế hệ trước. Các thiết bị PCIe 6.0 bắt đầu được bán ra thị trường vào tháng 4 từ Renesas. Tuy nhiên, sẽ còn một thời gian nữa chúng ta mới thấy các thiết bị như SSD và GPU hỗ trợ giao diện tốc độ này - các thông số kỹ thuật này thường được phê duyệt và hoàn thiện rất lâu trước khi chúng ta thấy silicon xuất xưởng.

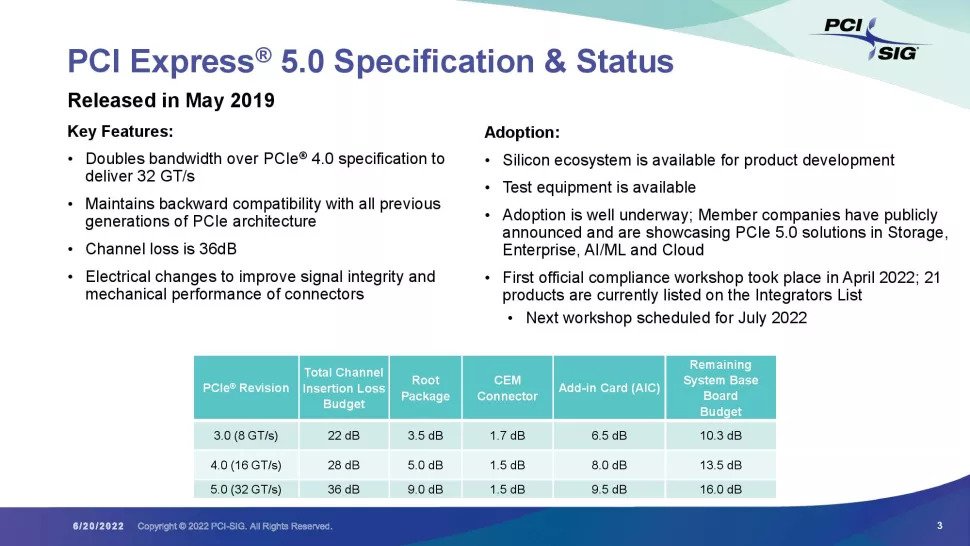

Như bạn sẽ thấy, vẫn chưa có nhiều thiết bị PCIe 5.0 trên thị trường, mặc dù giao diện này đã xuất hiện trên các bo mạch chủ phổ thông với Alder Lake của Intel và cũng sẽ xuất hiện trên nền tảng Zen 4 Ryzen 7000 sắp ra mắt của AMD vào cuối năm nay. Các ổ SSD PCIe 5.0 đầu tiên sẽ đến cùng lúc với bộ vi xử lý Ryzen 7000, nhưng chúng tôi đã thấy các thông báo về sản phẩm dành cho thiết bị PCIe 5.0 dành cho trung tâm dữ liệu và thiết bị AI / ML.

Nói cách khác, bạn sẽ không thấy các thiết bị PCIe 7.0 trên thị trường trong một thời gian dài, mặc dù PCI-SIG đang bắt đầu xác định thông số kỹ thuật ngay bây giờ và hy vọng sẽ đạt được mục tiêu cung cấp thông số kỹ thuật mới sau mỗi ba năm. Thông số PCIe 7.0 dự kiến sẽ hạ cánh vào năm 2025, nhưng chúng ta sẽ không thấy các thiết bị cuối cho đến khung thời gian năm 2028.

PCIe 7.0 Specification Goals:

- Cung cấp tốc độ bit thô 128 GT / s và lên đến 512 GB / s hai chiều thông qua cấu hình x16

- Sử dụng tín hiệu PAM4 (Điều chế biên độ xung với 4 mức)

- Tập trung vào các thông số kênh và phạm vi tiếp cận

- Tiếp tục cung cấp các mục tiêu có độ trễ thấp và độ tin cậy cao

- Nâng cao hiệu quả sử dụng điện

- Duy trì khả năng tương thích ngược với tất cả các thế hệ công nghệ PCIe trước đây

PCI-SIG vẫn chưa chia sẻ nhiều chi tiết về giao diện, nhưng chúng tôi chắc chắn sẽ tìm hiểu thêm vì nó hoạt động theo cách của nó trong giai đoạn định nghĩa. Trong khi chờ đợi, đây là trang báo chí đầy đủ để bạn xem xét.

Nguồn: Tom's Hardware

Tin xem nhiều

Tin mới nhất

Đăng ký nhận thông báo từ NPCshop.vn Không bỏ lỡ hàng ngàn sản phẩm và các chương trình khuyến mãi khác

36 Nguyễn Khuyến, Phường Bình Thạnh, TP.HCM (Làm việc từ T2 - T7 lúc 9h đến 18h30)

[Xem đường đi]

CSKH: 0909.22.66.07

Bán hàng: 0967.434.407

kinhdoanh@npcshop.vn

GPĐKKD: số 0316248670 do Sở KHĐT

Tp.Hồ Chí Minh cấp ngày 28/04/2020

© 2021 NPCshop

![🔥 [12.12 SUPER SALE] MUA GHẾ FLAGSHIP – TẶNG PHÍM CƠ XỊN](/media/news/388-z7315844106610_9e13ffb8db2d22422dc4fa98c5b75ec2.jpg)